불 대수와 논리 게이트

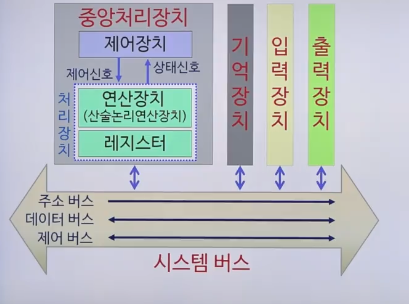

시스템 버스

중앙처리장치, 기억장치, 입출력장치 간의 물리적 연결 및 데이터 교환의 통로

주소 버스

- CPU가 기억장치나 입출력장치의 주소 정보를 전송하는 신호선의 집합

- 버스의 폭이 시스템의 메모리 용량을 결정 → n개의 신호선으로는 2^n개의 주소 지정 가능

- 단방향 버스

데이터 버스

- CPU와 기억장치/입출력장치 사이에 데이터 전송을 위한 신호선 집합

- 버스의 폭이 한 번에 전송할 수 있는 비트의 수를 의미 → 워드

- 양방향 버스

제어 버스

- CPU가 각종 장치의 동작을 제어하기 위한 다양한 신호들의 통로

- 버스의 폭(=제어신호의 수)은 CPU나 시스템의 구성에 따라 달라짐

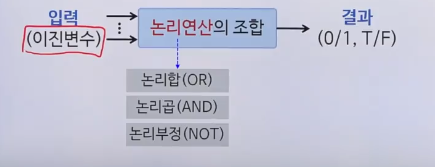

불 대수

이진 변수의 논리 연산을 다루는 대수

- 영국의 수학자 George Boole

- 논리적 문제를 해결하기 위한 수학적 방법 → 논리 대수, 스위칭 대수

- 논리 게이트: 논리 연산을 하드웨어로 구현한 것

- 논리 게이트의 완전 집합: 원하는 임의의 회로를 구성할 수 있는 게이트들의 부분 집합

- 불 대수의 기본 법칙

- 불 대수와 논리회로: 불 함수 ↔ 논리회로 형태로 표현 가능

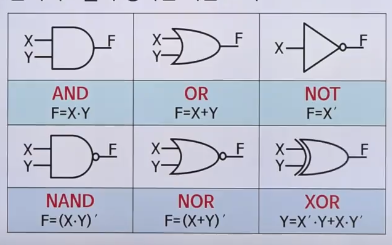

논리회로

논리 게이트들로 구성된 회로

조합회로(combination circuit)

- 출력값이 단순히 현재 입력값의 조합으로만 결정되는 회로

- 전가산기, 디코드, 인코더, 멀티플렉서, 디멀티플렉서 등 주로 연산을 위해서 사용되는 회로

전가산기

Full Adder: 아랫자리에서 올라온 올림수(carry)를 고려한 가산기

- 가산기: 두 이진수를 입력받아서 더하는 회로

- 반가산기(Half Adder): 아랫자리의 올림수를 미고려한 가산기

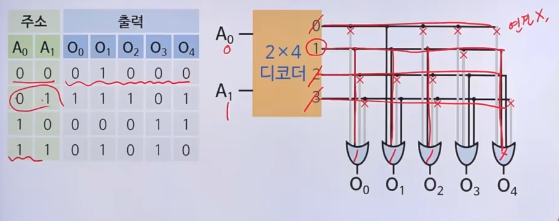

디코더

- n비트의 이진 코드를 최대 2^n개의 서로 다른 정보로 변환 → 출력 중에서 오직 한 개만 1이 되고, 나머지는 모두 0이 됨

- 주소 방식으로 주어진 입력으로부터 각각의 하드웨어 구성 요소를 개별적으로 구동하기 위해 주로 사용

→ 주기억장치에 접근할 때도 디코더의 기본 원리가 그대로 적용

멀티플렉서

- 여러 개의 입력선 중에서 하나를 선택하여 단일의 출력으로 내보내는 회로(데이터 선택기)

- 어떤 장치(회로)로부터 들어오는 데이터가 버스를 사용할 것인가를 정하는 경우에 사용

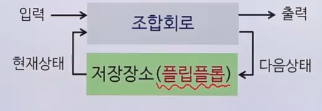

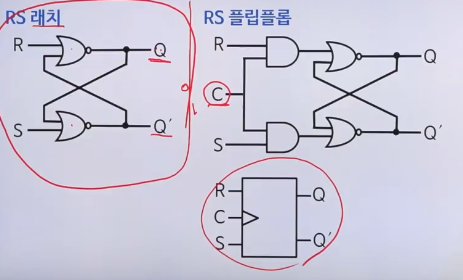

순서회로(sequential circuit)

- 연산의 각 단계마다 회로의 특정 상태가 저장/참조되는 회로 → 출력값이 입력값과 기억소자에 저장된 현재 상태에 따라 결정

- 카운터, 레지스터 등

플립플롭

1비트의 이진 정보를 저장할 수 있는 장치

- 입력신호에 의해서 상태를 바꾸도록 지시할 때까지는 현재의 이진 상태를 유지하는 논리소자

- 종류(입력의 개수와 상태를 변화시키는 방법에 따라)

- RS(Reset-Set) 플립플롭

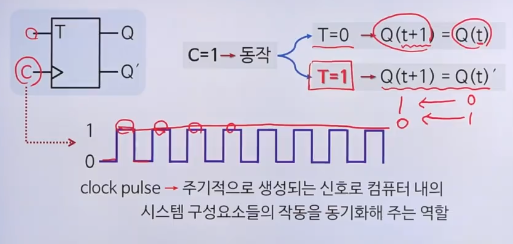

- T(Toggle) 플립플롭

카운터

클록펄스가 입력될 때마다 미리 정해진 순서에 따라 상태가 변하는 장치

- 매번 구동 시마다 저장된 이진수가 1씩 증가하는 장치

- 외부에서의 입력/출력이 없으며 클록펄스를 통해서만 상태가 변함

기억장치

ROM(Read Only Memory)

- 내용이 항상 고정되어 있어 조합회로로 구성 가능(읽기 전용)

- 설계자가 저장되는 이진 정보를 결정하고, 필요한 내부 연결 패턴을 기억장치 내에서 형성하여 구현

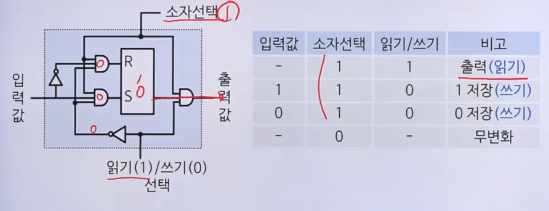

RAM(Random Access Memory)

- 상태를 저장하고 변경할 수 있는 순차회로로 구성 가능(읽기/쓰기가 모두 가능)

- DRAM(Dynamic RAM)

- 플립플롭이 아닌 축전지로 구현

- 시간이 지남에 따라 전류가 방전되므로 주기적인 refresh 과정 필요

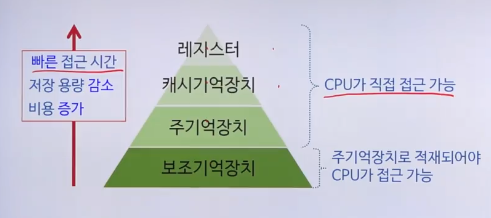

기억장치의 계층 구조

- 접근 속도와 저장 용량에 따라 계층적인 분류 가능: CPU가 데이터에 접근함에 있어서 가장 적은 비용으로 가장 높은 성능을 얻기 위한 전략

- 참조의 지역성(locality of reference)

- 공간의 지역성: 다음 순간에 접근할 위치는 현재의 접근 위치와 근접해 있을 가능성이 큼

- 시간적 지역성: 최근에 접근한 위치들이 가까운 미래에 다시 접근할 가능성이 큼

- 레지스터: CPU 내부에 존재하여 각종 연산에서 직접적으로 사용

- 캐시기억장치: CPU와 주기억장치 간의 속도 차이를 줄여주는 역할

- CPU와 주기억장치 사이에 위치한 접근 속도가 빠른 소규모 기억장치

- 수행 중인 명령어와 자주 사용되는 데이터를 저장하였다가 CPU 요청이 있을 경우 즉시 제공

- 주기억장치: 현재 수행 중인 프로그램과 데이터를 저장

- 보조기억장치

- 반영구적인 저장

- 사용을 위해서는 주기억장치에 적재되어야 함

명령어

명령어 집합 구조

- 내장 프로그램 개념으로부터 직접적으로 도출된 개념

- ISA, Instruction Set Architecture

- 명령어 집합

- 컴퓨터 시스템 내에 정의되어 있는 기본적인 명령어들의 집합

- 명령어 종류, 명령어 형식, 주소지정방식 등을 고려해서 결정

- 명령어 집합이 정의되면 상응하는 하드웨어 구조가 결정됨

복합 명령어 집합 컴퓨터(CISC, Complex Instruction Set Computer)

복합 명령어를 포함하여 명령어와 주소지정방식의 수를 많이 사용

- 프로그램에서 사용되는 전체 명령어의 수를 줄여서 프로그램의 실행 시간 단축

- 연산 코드 해석 및 실행을 위한 제어장치가 복잡해지는 단점

단축 명령어 집합 컴퓨터(RISC, Reduced Instruction Set Computer)

명령어를 단순화하고 개수를 줄여서 하드웨어를 개선시킨 구조

- 각 명령어의 길이를 가능한 짧게 함으로써 각 명령어의 실행 시간을 최소화 → 많은 처리량과 빠른 속도 지향

- 제어장치는 비교적 간단하며, 일반적으로 하드웨어로 구성

명령어 종류

- 데이터 전송 명령어: 데이터 이동(레지스터 ↔ 레지스터, 주기억장치 ↔ 레지스터, 기억장치 ↔ 기억장치 등)

- 데이터 처리 명령어: 산술 명령어, 논리연산 명령어, 비트 단위 명령어, 시프트 명령어 등

- 프로그램 제어 명령어: 프로그램의 제어 흐름 관리 → 무조건적 분기, 조건적 분기

- 입출력 명령어: 보조기억장치, IO장치 등과의 정보 교환 명령어, 인터럽트(프로그램의 정상 수행을 잡시 멈추고, CPU 이외의 다른 장치의 요구 사항을 수행하는 기능) 관련 명령어

명령어 형식

각 명령어는 실행에 필요한 모든 정보를 포함해야 함

- 연산자 코드(OP Code): CPU가 처리할 연산의 종류

→할당된 비트 수: CPU가 수행할 수 있는 명령의 최대 개수 - 오퍼랜드(operand, 피연산자): 멸령어가 사용할 데이터 또는 데이터가 저장되어 참조될 기억장치의 주소

- 오퍼랜드의 개수는 컴퓨터 구조에 따라 달라짐

- 연산의 대상이 되는 데이터가 어디서 추출되고, 결과가 어디에 저장할 지에 따른 구분

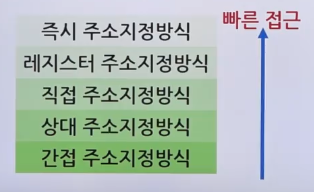

주소지정방식

연산에 사용될 데이터가 기억장치의 어디에 위치하는지를 지정하는 방법(addressing mode)

→ 유효주소(effective address): 주소 지정방식에 의해 계산되어 실제 데이터가 저장된 주소

중앙처리장치

명령어의 구현 방법

마이크로 프로그램에 의한 제어장치(micro-programmed control device)

- 연산과 명령어 수행 순서 조작 회로가 제어기억장치에 저장된 비트 패턴(마이크로 연산)으로 기동하는 장치

- 각 명령어는 여러 개의 마이크로 연산으로 구현

- 명령어 세트의 변경이나 명령어 추가 등이 용이

- CISC 컴퓨터 구조에서 주로 사용

직접 회로로 구성된 제어장치(hard-wired control device)

- 연산과 명령어 수행 회로가 기억장치에 의존하지 않고 직접 구성된 제어 회로에 의해 기동되는 장치

- 빠른 수행, 멸령어 세트의 변경에 쉽게 적응할 수 없음

- 명령어 수가 적은 RISC 컴퓨터 구조에서 주로 사용

레지스터

특수 레지스터

- AC(누산기, accumulator): 데이터 연산 결과를 일시적으로 저장하는 레지스터 → CPU의 연산 결과는 반드시 누산기에 저장

- MAR(기억장치 주소 레지스터, Memory Address Register): 현재 PC의 내용(다음에 수행될 명령어가 저장되어 있는 기억장소의 주소) 시스템 버스의 주소 버스로 출력되기 전에 일시적으로 저장

- MBR(기억장치 버퍼 레지스터, Memory Buffer Register): 기억장치에 저장될 또는 기억장치에서 읽어온 데이터를 임시적으로 저장

제어단어(control word)

- 각 비트들이 처리장치의 논리회로 내의 각종 MUX와 디코더의 선택 제어선으로 연결되어 하드웨어를 직접적으로 통제

- 각 마이크로 연산은 제어단어로 일대일 매핑되어 있음

제어장치

메모리에 저장된 명령을 어떻게 순차적으로 가져와서 수행할 것인가를 통제하는 부분

- 처리장치를 구동해서 특정 연산을 수행한 후 처리장치 내의 레지스터 값을 갱신하고 연산 결과를 출력

- 현재 명령을 수행한 후 다음에 수행할 멸령의 주소 정보를 생성

명령어 사이클(instruction cycle)

- PC(프로그램 카운터, Program Counter): 다음에 수행될 명령어가 저장되어있는 주기억장치의 주소를 저장하고 있는 레지스터

- IR(명령어 레지스터, Instruction Register): 기억장치에서 가져와서 현재 실행 중인 명령어를 저장하고 있는 레지스터

- 제어장치(control memory): 마이크로연산의 집합을 저장하고 있는 기억장치(ROM으로 구현)

- 명령어 해독기: 주어진 명령어를 제어기억장치의 해당 마이크로명령이 시작하는 주소로 매핑해주는 것

- 주소 결정회로: 명령어에 포함된 주소 정보, 제어단어와 연결된 주소 정보, 처리장치 구동 후 결과로 나오는 상태 비트 등으로부터 제어기억장치의 다음 수행할 마이크로 명령의 주소를 생성

- 제어기억장치 주소 레지스터(CMAR): 제어기억장치에서 다음에 수행할 마이크로 명령의 위치를 가리키는 주소를 저장

- 제어기억장치 데이터 레지스터(CMDR)

- 제어기억장치에서 가져온 다음 수행할 마이크로연산을 저장

- CMDR 없이 제어기억장치의 출력이 직접 다른 장치들로 연결될 수 있음

입출력장치 및 병렬처리

입출력 시스템

- 입출력장치: 사용자와 컴퓨터 시스템을 연결해주는 장치

- 입출력장치 제어기: 상이한 기계적/전자적 특성을 가진 입출력장치를 물리적/전자적으로 제어해서 구동시키는 작업을 수행하는 기기

- 모터 회전, 헤드 이동, 입출력 매체의 위치 정렬 등의 작접

- 제어기가 입출력장치에 포함된 경우, 하나의 제어기로 여러 입출력장치를 제어하는 경우도 존재

- 입출력장치 인터페이스: 입출력장치와 중앙처리장치/주기억장치 사이의 데이터 전송 속도, 데이터 처리 단위, 오류 확률의 차이를 상쇄해서 올바른 전송 방법을 제공

- 입출력 버스

- 입출력 전용으로 사용되는 정보 회선을 묶음 → 입출력장치와 중앙처리장치 상이의 정보 교환에 사용

- 여러 장치에 의한 버스 사용 충돌을 막기 위한 중재기가 필요

입출력 제어 방식

CPU에 의한 제어

독립된 입출력 제어기 없이 입출력 장치의 정보가 CPU를 통해 주기억장치에 쓰고 읽혀지는 방식

- 프로그램에 의한 방식: CPU가 주기적으로 입출력장치에 신호를 보내 입출력 여부를 물어보는 방식

- 인터럽트에 의한 방식: 입출력장치가 인터럽트를 통ㅎ래 입출력 요청이 있을 때만 CPU가 하던 일을 중단하고 해당 장치와 연락하는 방식

DMA(Direct Memory Access) 방식

- 입출력장치가 주기억장치와 직접 연결

- CPU는 두 장치 간의 초기 설정 및 허가에만 관여

- 직접적인 정보의 이동은 장치 간에 DMA 제어기가 해결

채널 방식

- 채널(입출력 전용의 별도 프로세서) 사용

- 정보 전송 통로 제공 및 CPU와 같은 산술/논리/분기 연산 작업도 수행 가능

병렬처리

파이프라인 처리기(pipeline processor)

- 프로그램 내에 내재하고 있는 시간적 병렬성을 활용

→ CPU내의 하드웨어 요소의 일부를 파이프라인 형태로 구성하여 프로그램 수행에 필요한 작업을 시간적으로 중첩하여 수행시키는 처리기 - 하나의 연산을 서로 다른 기능을 가진 여러 개의 단계로 분할하여, 각 단계가 동시에 서로 다른 데이터를 취급하도록 함

- 현재 명령의 특정 단계가 끝나고 다음 단계로 넘어가면 바로 다른 명령을 불러들여서 해당 단계를 동시에 처리하는 방식

- 연달아 수행될 명령어들이 서로 간에 간섭이 없어야 함

멀티코어(multicore) 구조

하나의 CPU에 2개 이상의 코어를 넣어서 동시에 여러 개의 명령어를 처리할 수 있는 구조

- 코어: CPU의 일부분으로 명령을 가져와 수행하는 주회로

- 각 코어는 수행 중인 응용 프로그램의 프로세스나 스레드를 하나씩 담당

GPGPU(General Purpose Computing on Graphics Processing Unit)

- 그래픽스 처리 장치를 사용한 범용 연산

- 그래픽 카드의 고도의 병렬처리 능력을 연산에 사용하는 기술

'CS' 카테고리의 다른 글

| [컴퓨터과학개론] 데이터베이스 (0) | 2023.12.04 |

|---|---|

| [컴퓨터과학개론] 프로그래밍 언어 (0) | 2023.12.04 |

| [프로그래밍 언어론] 복합타입 (0) | 2023.12.01 |

| [프로그래밍 언어론] 타입 (0) | 2023.12.01 |

| [프로그래밍 언어론] 변수의 영역 (0) | 2023.12.01 |

![[컴퓨터과학개론] 컴퓨터 구조](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2F0PARj%2FbtsBjqvjJK9%2FAAAAAAAAAAAAAAAAAAAAAPp10O2DE0SmYqnb1_hne_7mSqMUsgesY6ngzCaZte5E%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DgJHc%252FdKgE3a1J42EMvBJnrLjN3I%253D)